VHDL - 4-bit adder using half and full adder

VHDL module program:

1. Half adder component:

library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity H_A is Port ( a : in STD_LOGIC; b : in STD_LOGIC; sum : out STD_LOGIC; carry : out STD_LOGIC); end H_A; architecture Behavioral of H_A is begin sum<=a xor b; carry<=a and b; end Behavioral;

2. Full adder component:

library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity F_A is Port ( a : in STD_LOGIC; b : in STD_LOGIC; c : in STD_LOGIC; sum : out STD_LOGIC; carry : out STD_LOGIC); end F_A; architecture Behavioral of F_A is begin sum<=a xor b xor c; carry<=((a and b) or (b and c) or (a and c)); end Behavioral;

3. 4-bit adder:

library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity adder_4_bit is Port ( a : in STD_LOGIC_VECTOR (3 downto 0); b : in STD_LOGIC_VECTOR (3 downto 0); sum : out STD_LOGIC_VECTOR (3 downto 0); carry : out STD_LOGIC); end adder_4_bit; architecture Behavioral of adder_4_bit is component H_A is port (a : in STD_LOGIC; b : in STD_LOGIC; sum : out STD_LOGIC; carry: out STD_LOGIC ); end component; Component F_A is port (a : in STD_LOGIC; b : in STD_LOGIC; c : in STD_LOGIC; sum : out STD_LOGIC; carry: out STD_LOGIC ); end component; signal s : std_logic_vector (2 downto 0); begin u0 : H_A port map (a(0),b(0),sum(0),s(0)); u1 : F_A port map (a(1),b(1),s(0),sum(1),s(1)); u2 : F_A port map (a(2),b(2),s(1),sum(2),s(2)); u3 : F_A port map (a(3),b(3),s(2),sum(3),carry); end Behavioral;

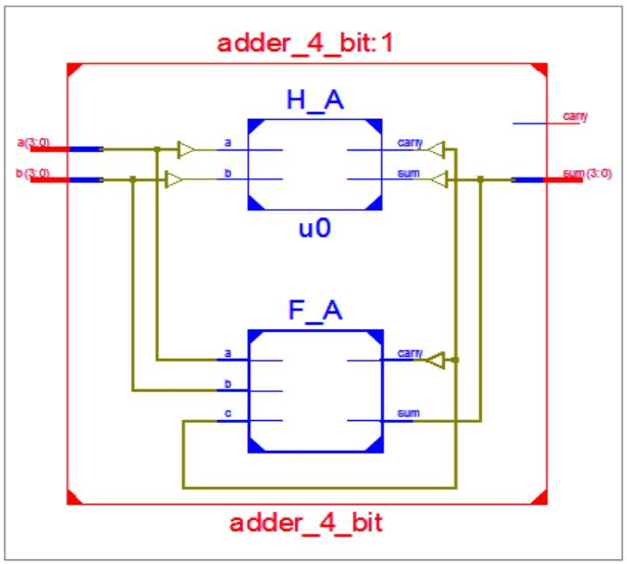

Register - Transfer - Level schematic:

VHDL Test bench program:

LIBRARY ieee; USE ieee.std_logic_1164.ALL; ENTITY adder_4bit_tb IS END adder_4bit_tb; ARCHITECTURE behavior OF adder_4bit_tb IS COMPONENT adder_4_bit PORT( a : IN std_logic_vector(3 downto 0); b : IN std_logic_vector(3 downto 0); sum : OUT std_logic_vector(3 downto 0); carry : OUT std_logic ); END COMPONENT; signal a : std_logic_vector(3 downto 0) := (others => '0'); signal b : std_logic_vector(3 downto 0) := (others => '0'); signal sum : std_logic_vector(3 downto 0); signal carry : std_logic; BEGIN uut: adder_4_bit PORT MAP ( a => a, b => b, sum => sum, carry => carry ); stim_proc: process begin wait for 100 ns; a<="1001"; b<="1000"; wait for 100 ns; a<="1001"; b<="0010"; wait for 100 ns; a<="1001"; b<="0110"; wait; end process; END;

VHDL Test bench:

Comments

Post a Comment