Logic Gates - VHDL

AND gate:

VHDL module program:

Register - Transfer - Level schematic:

Technology schematic:

VHDL Test bench program

VHDL Test bench:

VHDL module program:

library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity and_ab is Port ( a : in STD_LOGIC; b : in STD_LOGIC; c : out STD_LOGIC); end and_ab; architecture Behavioral of and_ab is begin c<=a and b; end Behavioral;

Register - Transfer - Level schematic:

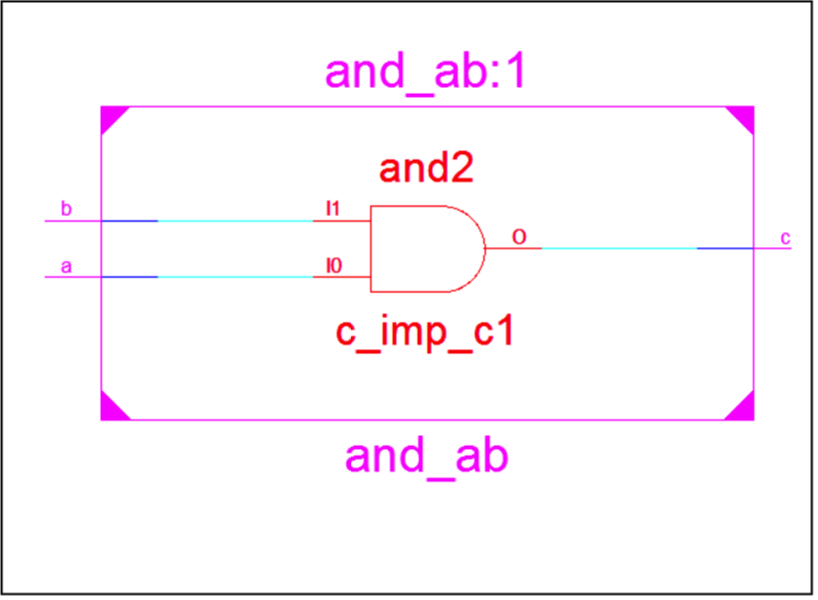

Technology schematic:

VHDL Test bench program

LIBRARY ieee; USE ieee.std_logic_1164.ALL; ENTITY a IS END a; ARCHITECTURE behavior OF a IS COMPONENT and_ab PORT( a : IN std_logic; b : IN std_logic; c : OUT std_logic ); END COMPONENT; signal a : std_logic := '0'; signal b : std_logic := '0'; signal c : std_logic; BEGIN uut: and_ab PORT MAP ( a => a, b => b, c => c ); stim_proc: process begin a<='0'; b<='0'; wait for 300 ns; a<='0'; b<='1'; wait for 100 ns; a<='1'; b<='0'; wait for 100 ns; a<='1'; b<='1'; wait for 100 ns; wait; end process; END;

VHDL Test bench:

Comments

Post a Comment